# University of California, Santa Barbara

Department of Electrical and Computer Engineering

ECE 152A – Digital Design Principles

Homework #7

### Problem #1.

For the function below:

$$F(A,B,C) = \Sigma m (1,2,4,5,7)$$

- (1) Express the function in standard (minimized) sum of products form

- (2) Construct a truth table for the function

- (3) Implement the function with a four-to-one multiplexer:

- (4) Using Shannon's expansion theorem, expand the function from part (1) above in terms of the variable A. Show all steps.

- (5) Implement the function with a two-to-one MUX and the minimum number of additional gates.

#### Problem #2.

In this problem you are to design a 4-bit barrel shifter (using TTL components) and determine its maximum frequency (minimum clock period) of operation.

Note: This problem consists of 4 parts. It is possible to do parts 3 and 4 without doing parts 1 and 2.

A barrel shifter allows rotating the contents of a register an arbitrary number of bits to the left or right. If the bits in this register are labeled A, B, C and D the operation of the barrel shifter is as shown below:

| Shift Direction | <u>Count</u> | Re | egister | Contents Contents |   |

|-----------------|--------------|----|---------|-------------------|---|

| Right           | 0            | Α  | В       | С                 | D |

| Right           | 1            | D  | Α       | В                 | С |

| Right           | 2            | С  | D       | Α                 | В |

| Right           | 3            | В  | С       | D                 | Α |

| Left            | 0            | Α  | В       | С                 | D |

| Left            | 1            | В  | С       | D                 | Α |

| Left            | 2            | С  | D       | Α                 | В |

| Left            | 3            | D  | Α       | В                 | С |

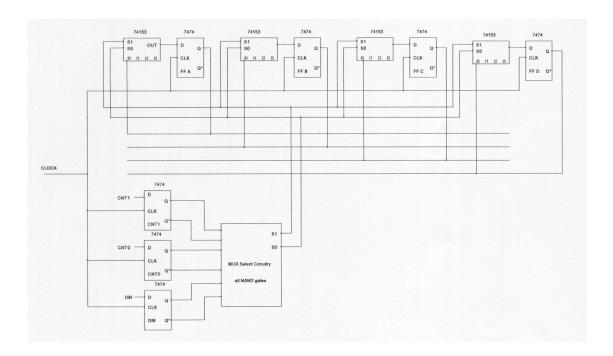

The barrel shifter can be constructed using four D flip-flops and four 4:1 multiplexers, one on the D input of each flip-flop. Given a 3 bit control word indicating the direction (DIR: 0 = right and 1 = left) and count (CNT1, CNT0: 00 = 0, 01=1,10=2 and 11 =3), a combinational circuit (MUX select circuitry) generates the select inputs (S1 and S0) for the four multiplexers. The same S1 and S0 are applied to all four multiplexers, selecting the correct input to the D flip-flop.

The implementation of the barrel shifter will use 7474 D flip-flops, 74153 4:1 multiplexers and assorted NAND gates (7400, 7410, 7420, 7430). The relevant timing data is provided below.

### 7474

|                                   |                     | SERIES 54/74 |      | '70 |      |      | 72, '73<br>76, '10 |      |      | '74 |      |      | '109 |      |      | '110 |      |      | '111 |      | UNI |

|-----------------------------------|---------------------|--------------|------|-----|------|------|--------------------|------|------|-----|------|------|------|------|------|------|------|------|------|------|-----|

|                                   |                     |              | MIN  | NOM | MAX  | MIN  | NOM                | MAX  | MIN  | NOM | MAX  | MIN  | NOM  | MAX  | MIN  | NOM  | MAX  | MIN  | NOM  | MAX  |     |

| Cupply voltage Van                |                     | Series 54    | 4.5  | 5   | 5.5  | 4.5  | 5                  | 5.5  | 4.5  | 5   | 5.5  | 4.5  | 5    | 5.5  | 4.5  | 5    | 5.5  | 4.5  | 5    | 5.5  | V   |

| Supply voltage, VCC               |                     | Series 74    | 4.75 | 5   | 5.25 | 4.75 | 5                  | 5.25 | 4.75 | 5   | 5.25 | 4.75 | 5    | 5.25 | 4.75 | 5    | 5.25 | 4.75 | 5    | 5.25 |     |

| High-level output curre           | nt, IOH             |              |      |     | -400 |      |                    | -400 |      |     | -400 |      |      | -800 |      |      | -800 |      |      | -800 | μА  |

| Low-level output curre            | nt, IOL             |              |      |     | 16   |      |                    | 16   |      |     | 16   |      |      | 16   |      |      | 16   |      |      | 16   | mA  |

|                                   | Clock high          |              | 20   |     |      | 20   |                    |      | 30   |     |      | 20   |      |      | 25   |      |      | 25   |      |      |     |

| Pulse width, tw                   | Clock low           |              | 30   |     |      | 47   |                    |      | 37   |     |      | 20   |      |      | 25   |      |      | 25   |      |      | ns  |

|                                   | Preset or clear lov | v            | 25   |     |      | 25   |                    |      | 30   |     |      | 20   |      |      | 25   |      |      | 25   |      |      |     |

| Input setup time, t <sub>su</sub> |                     |              | 201  | 100 |      | 01   |                    |      | 201  |     |      | 101  |      |      | 201  |      |      | 01   |      |      | ns  |

| Input hold time, th               |                     |              | 51   |     |      | 01   |                    |      | 51   |     |      | 61   |      |      | 51   |      |      | 301  |      |      | ns  |

|                                   |                     | Series 54    | -55  |     | 125  | -55  |                    | 125  | -55  |     | 125  | -55  |      | 125  | -55  |      | 125  | -55  |      | 125  |     |

## 7474

| PARAMETER 9      | FROM<br>(INPUT) | TO (OUTPUT) | TEST                    |     | ′70 |     | 1   | 72, '73<br>76, '10 |     |     | '74 |     |     | '109 |     |     | 110 |     |     | '111 |     | UNI |

|------------------|-----------------|-------------|-------------------------|-----|-----|-----|-----|--------------------|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|------|-----|-----|

|                  | (1141 017       | 10011017    | CONDITIONS              | MIN | TYP | MAX | MIN | TYP                | MAX | MIN | TYP | MAX | MIN | TYP  | MAX | MIN | TYP | MAX | MIN | TYP  | MAX | -   |

| f <sub>max</sub> |                 |             |                         | 20  | 35  |     | 15  | 20                 |     | 15  | 25  |     | 25  | 33   |     | 20  | 25  |     | 20  | 25   |     | мн: |

| tPLH             | Preset          | Q           |                         |     |     | 50  |     | 16                 | 25  |     |     | 25  |     | 10   | 15  |     | 12  | 20  |     | 12   | 18  | -   |

| tPHL             | (as applicable) | ā           | CL = 15 pF,             |     |     | 50  |     | 25                 | 40  |     |     | 40  |     | 23   | 35  |     | 18  |     |     | 21   | 30  | ns  |

| tPLH             | Clear           | ā           | R <sub>L</sub> = 400 Ω, |     |     | 50  |     | 16                 | 25  |     |     | 25  |     | 10   | 15  |     | 12  | 20  |     | 12   | 18  | -   |

| tPHL             | (as applicable) | Q           | See Note 2              |     |     | 50  |     | 25                 | 40  |     |     | 40  |     | 17   | 25  |     | 18  |     |     | 21   | 30  | ns  |

| tPLH             | CII             |             |                         |     | 27. | 50  |     | 16                 | 25  |     | 14  | 25  |     | 10   | 16  |     | 20  | 30  | -   | 12   | 17  | -   |

| tPHL             | Clock           | Q or Q      |                         |     | 18  | 50  |     | 25                 | 40  |     | 20  | 40  |     | 18   | 28  |     | 13  | 20  |     | 20   | 30  | ns  |

¶f<sub>max</sub> = maximum clock frequency; tp\_H = propagation delay time, low-to-high-level output; tp<sub>HL</sub> = propagation delay time, high-to-low-level output. NOTE 2: Load circuit and voltage waveforms are shown on page 3-10.

## 74153

| PARAMETER¶ | FROM<br>(INPUT) | TO (OUTPUT) | TEST CONDITIONS                                 | MIN | TYP | мах | UNIT |

|------------|-----------------|-------------|-------------------------------------------------|-----|-----|-----|------|

| tPLH       | Data            | Y           |                                                 |     | 12  | 18  | ns   |

| tPHL       | Data            | Y           |                                                 |     | 15  | 23  | ns   |

| tPLH       | Select          | Y           | C <sub>L</sub> = 30 pF, R <sub>L</sub> = 400 Ω, |     | 22  | 34  | ns   |

| tPHL       | Select          | Y           | See Note 3                                      |     | 22  | 34  | ns   |

| 4          | Ctrobo          |             |                                                 |     | 10  | 30  | ne.  |

# 7400, 7410, 7420, 7430

| TYPE     | TEST<br>CONDITIONS#                            |     | tpLH (ns)<br>egation delay<br>o-high-level o |     | tpHL (ns) Propagation delay time, high-to-low-level output |     |     |  |  |

|----------|------------------------------------------------|-----|----------------------------------------------|-----|------------------------------------------------------------|-----|-----|--|--|

|          |                                                | MIN | TYP                                          | MAX | MIN                                                        | TYP | MAX |  |  |

| '00, '10 |                                                |     | 11                                           | 22  |                                                            | 7   | 15  |  |  |

| '04, '20 | C <sub>L</sub> = 15 pF, R <sub>L</sub> = 400 Ω |     | 12                                           | 22  |                                                            | 8   | 15  |  |  |

| '30      |                                                |     | 13                                           | 22  |                                                            | 8   | 15  |  |  |

|          |                                                |     |                                              |     |                                                            |     |     |  |  |

1. Complete the schematic below by showing the connections between the outputs of the four flip flops and the inputs to the four multiplexers necessary to realize the barrel shifter. The multiplexers should get all four flip-flop outputs; the problem is which input gets which one (S1S0 = 00: input = 10, 01 = 11, 10 = 12, 11 = 13). When there is no shift, the output of the flip-flop is fed back to the input of the same flip flop (as shown on the schematic).

- 2. The count and direction inputs are applied to the MUX select circuitry via 7474 D flip flops, hence both the true and complemented versions will be available (inverters not required). Based on the connections defined in part 1, design the MUX select circuitry using only NAND gates. Include Karnaugh maps and the minimized Boolean equations; you do not have to draw the schematic.

- 3. Determine the critical path in the design. (Note again: if you were unable to complete parts 1 and 2 above, you can assume that the MUX select circuitry can be realized via a 2-level NAND/NAND implementation).

- 4. Determine the minimum clock period for the design.

#### Problem #3.

In this problem you are asked to design a circuit that takes as its input, a three bit number (In2, In1, In0) and produces its complement (Out2, Out1, Out0). The input number can be in unsigned, sign magnitude, 1's complement or 2's complement representation. A 2-bit control input (Cntrl1, Cntrl0) indicates the representation of the input number as follows:

Cntrl1, Cntrl0 = 00 = unsigned 01 = sign magnitude 10 = 1's complement 11 = 2's complement

If the number is unsigned, the output of the circuit is the number itself (it has no complement). In all other cases, the output should be the complement of the input in the appropriate representation.

- 1. Implement the design using a ROM. Define the contents of each ROM location and clearly indicate how the ROM address is constructed.

- Ignoring (for the moment) the 2's complement portion of the design (Cntrl1, Cntrl0 = 11), redesign the circuit using 3, 4-to-1 multiplexers (i.e., generate the unsigned, sign magnitude and 1's complement numbers).

You can assume that both the true and complemented versions of In2, In1 and In0 are available (no inverters are necessary)

- Adding three full adders and a single AND gate to the design in part 2, complete the design to generate the 2's complement of the number (Cntrl1, Cntrl0 = 11).

#### Problem #4.

In this problem you are to design a two-bit, combinational comparator. The circuit has two, two-bit inputs A (A1, A0) and B (B1, B0) and three outputs A<B, A=B and A>B. Assume both A and B are unsigned integers and can take on the values 0 through 3. A1 and B1 are the more significant bits.

- 1. Design the circuit using an appropriately sized ROM. Show the contents of each memory location in the ROM

- Design the circuit using a decoder with high true outputs (again, of the appropriate size) and OR gates. Use sum of minterm notation in constructing your solution.